# Design of 16 Bit Carry Look Ahead Adder Using Reversible Logic

## Shailja Shukla, Tarun Verma and Rita Jain

Department of Electronic and Communication Engineering, LNCT, Bhopal, (MP), India

(Corresponding author Shailja Shukla) (Received 05 February, 2014 Accepted 17 April, 2014)

ABSTRACT: The demand of low power high speed circuits are in demand with the increasing universal growth in electronic system and the loss of information is not acceptable as with single loss of a bit information the energy loss is equal to kTlog2 joules/bit. Reversible logic can be of prominent interest to design low power arithmetic and data path units for digital signal processing applications, such as the designs of low power adders, multipliers, FFT, IDCT etc, and quantum computers. Quantum logic gates perform an elementary unitary operation and any unitary operation is reversible, hence quantum networks effecting elementary arithmetic operations must be built from reversible logic components. Thus, reversible logic will also be the immediate requirement to solve DSP problems with quantum computers. And the lowest processing units are adder and subtractor to perform any operation in digital world so in this paper I proposed a carry look ahead adder using reversible logic. And is simulated using Micro-wind 3.1 too on 90nm technology. The delay measured is 47nS and power consumed is .2mW and area acquired is 245µm².

#### I. INTRODUCTION

Reversible computation in a system can be performed only when the system comprises of reversible gates. These circuits can generate unique output vector from each input vector, and vice versa, that is, there is a oneto-one mapping between input and output vectors. It has been shown that for irreversible logic computations, each bit of information lost generates kTln2 joules of heat energy, where k is Boltzmann's constant and T the absolute temperature at which computation is performed, since the amount of energy dissipated in a system bears a direct relationship to the number of bits erased during computation. Furthermore, voltage-coded logic signals have energy of Esig = ½CV2, and this energy gets dissipated whenever switching occurs in conventional (irreversible) logic implemented in modern CMOS technology. It has been shown that reversible logic helps in saving this energy using charge recovery process. The most prominent application of reversible logic lies in quantum computers.

A quantum computer will be viewed as a quantum network (or a family of quantum networks) composed of quantum logic gates; each gate performing an elementary unitary operation on one, two or more two-state quantum systems called qu-bits. Each qu bit represents an elementary unit of information; corresponding to the classical bit values 0 and 1. Any unitary operation is reversible and hence quantum networks effecting elementary arithmetic operations such as addition, multiplication and exponentiation

cannot be directly deduced from their classical Boolean counterparts (classical logic gates such as AND or OR are clearly irreversible). Thus, quantum arithmetic must be built from reversible logical components.

ISSN No. (Online): 2277-2626

# II. FUNDAMENTAL REVERSIBLE LOGIC GATES USED

There are three types of fundamental 2\*2 reversible logic gates. First, the square-root-of-not gates utilize the unitary operators to produce reversible logic calculations. The Controlled-V and the Controlled-V+gates are the two types of square-root-of-not gates. In both of these gates, when the control input is 0, the second input is propagated to the output. The corresponding unitary operator is propagated to the second output when the control input is 1, where the

unitary operation is V=

$$\frac{t+1}{2} \begin{pmatrix} 1 & -t \\ -t & 1 \end{pmatrix}$$

for the Controlled-V gate and is V+ =  $\frac{t+1}{2} \begin{pmatrix} 1 & -\frac{1}{t} \\ -t & 1 \end{pmatrix}$  for the Controlled-V+ gate. When two Controlled-V gates

Controlled-V gate and is V+= V-i 1 for the Controlled-V+ gate. When two Controlled-V gates are activated in series, they act as an inverter. The same holds for two Controlled-V+ gates in series. When a Controlled-V and Controlled-V+ gate are activated in series, they act as an identity.

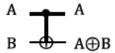

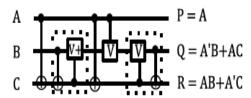

The second type of fundamental 2\*2 reversible-logic gate is the Feynman gate Fig 1, or the Controlled-Not gate. Proposed by Feynman, it is configured such that

its outputs states correlate to the input states in the following manner:

$$P = A$$

&  $Q = A XOR B$

Fig.1. Feynman logic gates.

The resulting value of the second output corresponds to the result of a conventional XOR gate. Since fan-out is expressively forbidden in reversible logic, since a fanout has one input and two outputs, the Feynman gate may be used to duplicate a signal when B is equal to 0. Its quantum configuration is shown in fig 2

Fig. 2. Quantum Representation of Feynman gate.

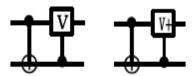

The third type of fundamental 2\*2 reversible logic gate is the integrated qubit gate. This gate is implemented with a Feynman gate with either a Controlled-V or Controlled V+ gate. The XOR output of the Feynman gate is used as the control signal for the Controlled-V or V+ gate it is coupled with. The quantum cost of the integrated qubit gate is 1 and its worst-case delay is 1. The quantum configurations of these gates are shown below in Fig.3

**Fig. 3.** Quantum Representations of Integrated Qubit Gates

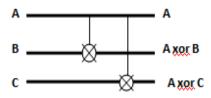

The 3\*3 New Fault Tolerant gate (NFT) with quantum cost of 5 is shown in fig.4 has worst case delay of 3 it has better correction capability The output states map to the inputs in this manner:

$$P = A XOR B$$

,  $Q = AC' XOR B'C$ , and  $R = AC' XORB C$ ,

Fig. 4. Quantum Representation of NFT gate.

The 3\*3 Feynman double gate gate with quantum cost of 2 is shown in fig 5. has worst case delay of 3 it has better correction capability

**Fig. 5.** Quantum Representation of F2G gate. The quantum cost is 5 and the worst-case delay is 5. The quantum representation is shown below in Fig.6

Fig. 6. Quantum Representation of Fredkin gate.

#### III. PROPOSED DESIGN

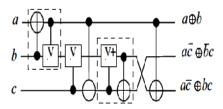

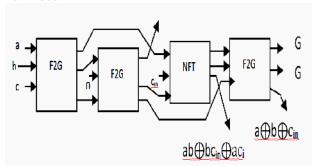

The proposed design of cost effective Reversible Fault Tolerant Full Adder by using New Fault Tolerant (NFT) and Feynman Double (F2G) gates. Then we have described the design of Fault Tolerant Carry Skip (RFT-CSA) and Carry Look-ahead (RFT-CLA) adders by using proposed design of Fault Tolerant Full Adder

**Single NFT Full Adder (SNFA)** is a Fault Tolerant full adder circuit which consists of one New Fault Tolerant (NFT) gate and three Feynman Double (F2G) gates where the quantum cost is 11 and the total number of garbage output is 3 (shown in Fig. 7). The minimum number of garbage bit to realize Reversible Fault Tolerant Full Adder circuit is 3

And proved as Let, *a*, *b* and *cin* are the inputs of a full adder circuit where *s* and *cout* are the corresponding outputs. There are three different states at the inputs (*a*, *b* and *cin*) where the outputs (*s* and *cout*) produce same patterns as shown in Table II. For any parity preserving reversible circuit, total number of EVEN or ODD parity at input or output is equal. Table II shows that the all input patterns are EVEN but the corresponding output patterns are ODD. Turning three ODD patterns at output into EVEN by adding two extra bits is not possible. Because two bits can represent 2<sup>2</sup> different states where 00 and 11 (01 and 10) are EVEN (ODD) only. So, Reversible Full Adder circuit requires at least 3 garbage bits to make itself Reversible Fault Tolerant Full Adder

**Fig. 7.** Proposed design of Fault Tolerant single NFT Full Adder (SNFA).

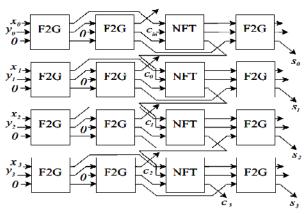

#### Fault Tolerant Carry Look-ahead Adder Circuit

This section introduces the design of Reversible Fault Tolerant Carry Look-ahead Adder (RFT-CLA) circuit overlaps the performance of all existing designs. Proposed design of RFT- CLA is based on New Fault Tolerant (NFT) and Feynman Double (F2G) gates where the carry is generated before sum. Reversible Fault Tolerant Carry Look ahead Adder (RFT-CLA) consists of serial attachment of n SNFAs but the work as a carry generator itself where the carry output of ith stage (ci) is produced before sum si where i= 0, 1, 2, ..., (n-1).n-bit RFT-CLA can be realized by using the combination of n NFTs and n F2Gs as shown in fig 8. The Delay of n-bit Reversible Fault Tolerant CLA (DRF T -CLA) can be minimized to (n+3). Proved as, the Delay of any circuit is the number of maximum gates laying on contiguous path of any input to output. The Delay of SNFA, DSNF A= 4 to generate sum not carry. Delay of parallel adder circuit depends on carry propagation (from c<sub>in</sub> to c<sub>out</sub>) of every stage. Any n-bits RFT-CLA needs n SNFAs where Delay of RFT-CLA, DRF T -FA = 4n. Because carry input (ci) of ith stage is generated by spending 1 units Delay where i = 0, 1, 2,..., (n-1). In first stage, extra two units Delay is added because of first carry output (c0) generation is related to operands at first stage. On the other hand, last stage has extra single unit Delay because the final sum is generated after one stage of generation of final carry (cout). So the Delay calculation for n-bits RFT-CLA is as follows:

$D_{RF\:T\:\text{-}FA}\!=n+3$  and fig 9 shows 16 bit RFT- CLA

**Fig. 8**. Proposed design of Reversible Fault Tolerant Carry Look ahead Adder with 12 garbage values.

**Fig. 9.** Efficient Design of 16- Reversible Fault Tolerant Carry Look-ahead Adder bit.

#### IV. SIMULATION RESULT

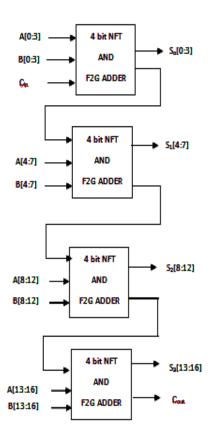

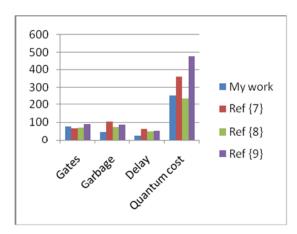

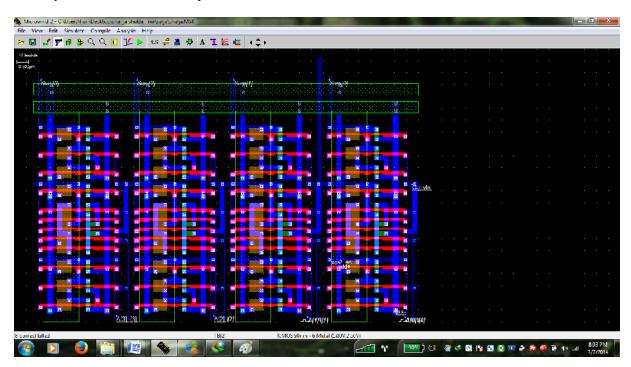

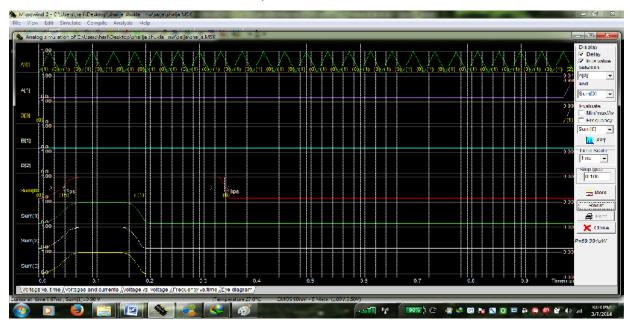

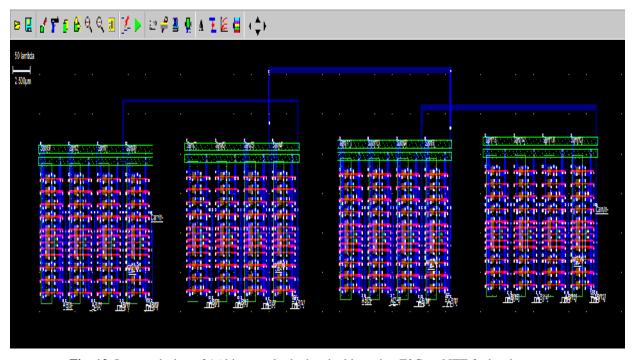

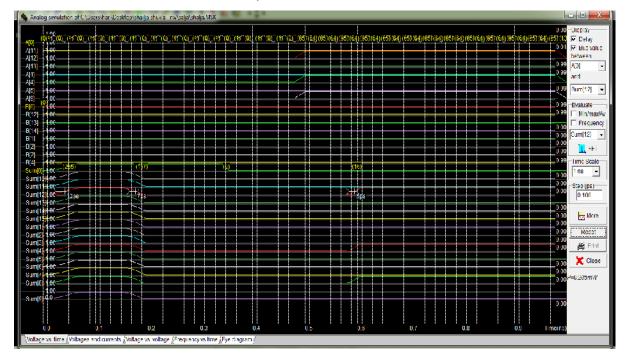

The above circuit is simulated in microwind 3.1 using 90nm CMOS technology The delay measured is 47nS and power consumed is .2mW and area acquired is  $245\mu\text{m}^2$  the quantum cost of CLA( carry look ahead adder) is 254 table 1shows the comparison with the other techniques of reversible logic to design the adder circuit. The Layout design of 4bit CLA and 16 bit CLA is shown in fig 10,12 simulation result were shown in fig 11.

#### V. FUTURE WORK

Now a day accuracy is the main goal to achieve with this fast processing environment and it will also consumes less energy , previous conventional circuits are non reversible and due to which during communication of data when there is loss of information circuit dissipates energy due to reload of data in between communication channel from input to output vectors. As reversibility recovers energy loss and prevent bit error by including fault tolerant mechanism. It is gaining much popularity in quantum computing, CMOS technology and DNA informatics. Now the main aim towards this technology is to achieve fault tolerant system and with increased speed.

So we have to make a circuit under optimized way in manner that it will be cost effective in the sense of Gate cost, delay, garbage and quantum cost taking all these in account we have to design the optimized circuit which are reversible and have capability to detect and correct the error during data transmission.

**Table 1** Comparison table between Proposed work, Ref{7}, Ref{8}, Ref{9} Ref{9} of CLA ADDER.

Fig. 10. Layout design of 4bit carry look ahead adder using F2G an NFT fault tolerant gates.

Fig. 11. Simulation result of 4 bit CLA adder.

Fig. 12. Layout design of 16 bit carry look ahead adder using F2G an NFT fault tolerant gates

Fig. 13. Simulation result of 4 bit CLA adder.

## REFERENCES

- [1]. Minimum Cost Fault Tolerant Adder Circuits in Reversible Logic Synthesis Sajib Kumar Mitra Ahsan Raja Chowdhury Faculty of Engineering and Technology University of Dhaka 2012 25th International Conference on VLSI Design IEEE.

- [2]. C.H. Bennett, "Logical reversibility of computation," IBM *Journal of Research and Development*, vol. **17**, pp. 525–532, 1973. A.

- [3]. K. Biswas, M.M. Hasan, A.R. Chowdhury, and H. M.H. Babu, "Efficient approaches for designing reversible binary coded decimal adders," *Microelectronics Journal*, vol. **39**, no. 12, pp. 1693–1703, December 2008.

- [4]. H.M.H. Babu and A.R. Chowdhury, "Design of a compact reversible binary coded decimal adder circuit," *Elsevier Journal Syst. Archit.*, vol. **52**, no. 5, pp. 272–282, January 2006.

- [5]. M.S. Islam, M.R. Islam, M.R. Karim, A.A.M. and H.M.H. Babu, "Minimization of adder circuits and variable block carry skip logic using reversible gates", *In Proc. of 7th International Conference on Computer and Information Technology, Dhaka, Bangladesh*, 26-28 December, 2004, pp. 378-383.

- [6]. M.S. Islam and M.R. Islam, "Minimization of reversible adder circuits", *Asian Journal of Information Technology*, vol. **4**, no. 12, pp. 1146-1151, 2005.

- [7]. H.M.H. Babu, M.R. Islam, A.R. Chowdhury, and S.M.A. Chowdhury, "Reversible logic synthesis for minimization of full-adder circuit," in *17th International Conference on VLSI design'04*. Mumbai, India, 2004, pp. 757–760.

- [8]. H. Thapliyal and M.B. Srinivas, "A novel reversible tsg gate and its application for designing reversible carry look-ahead and other adder architectures," in *Asia-Pacific Computer Systems Architecture Conference*, 2005, pp. 805–817.

- [9]. P.K. Lala, J.P. Parkerson, and P. Charaborty, "Adder designs using reversible logic gates," Wseas Transactions on Circuits and Systems, June 2010

- [10]. R. Landauer, "Irreversibility and heat generation in the computing process", *IBM J. Research and Development*, vol. **5**, pp. 183-191, 1961.

- [11]. C.H. Bennet, "Logical reversibility of computation", *IBM J. Research an Development*, vol. **17**, no. 6, pp. 525-532, 1973.

- [12]. M.S. Islam, M.R. Islam, M.R. Karim, A. A. Mahmud and H.M.H. Babu, "Variable block carry skip logic using reversible gates", *In Proc. of 10th International Symposium on Integrated Circuits, Devices & Systems, Singapore*, pp 9-12, 8-10 September, 2004.

- [13]. M.S. Islam, M.M. Rahman, Z. Begum and M.Z. Hafiz, "Low cost quantum realization of reversible multiplier circuit", Information Technology Journal, vol. 8, no. 2, pp.208-213, 2009.

- [14]. B. Parhami, "Fault tolerant reversible circuits", in Proceedings of 40th Asimolar Conf. Signals, Systems, and Computers, Pacific Grove, CA, pp. 1726-1729, October 2006.

- [15]. M.S. Islam, M.M. Rahman, Z. begum, and M.Z. Hafiz, "Efficient approaches for designing fault tolerant reversible carry look-ahead and carry-skip adders," MASAUM Journal of Basic and Applied Sciences, vol. 1, no. 3, 2009.

- [16]. J.W. Bruce, "Efficient adder circuits based on a conservative reversible logic gates," in ISVLSI '02: *Proceedings of the IEEE Computer Society Annual Symposium on VLSI. Washington*, DC, USA, 2005, pp. 83–88.

- [17]. M. Haghparast and K. Navi, "Design of a novel fault tolerant reversible full adder for nanotechnology based systems," *World Applied Science Journal*, vol. 3, no. 1, pp. 114–118, 2008.

- [18]. B. Desoete and A.D. Vos, "A reversible carry-look-ahead adder using control gates," *Intregation the VLSI Journal*, vol. **33**, no. 1, pp. 89–104, 2002.

- [1]. J. Lim, D. Kim, and S. Chae, "A 16-bit carry-lookahead adder using reversible energy recovery logic for ultra-low-energy systems," *IEEE J. Solid-State Circuits*, vol. **34**, pp. 898–903, 1999.

- [19]. E. Fredkin and T. Toffoli, "Conservative logic," *International Journal Of Theoretical Physics*, vol. **21**, pp. 219–253, 1982.

- [20]. M. Haghparast and K. Navi, "Novel fault tolerant gate for nanotechnology based systems," *American Journal of Applied Sciences*, vol. **5**, no. 5, pp. 519–523, 2008.